### (e) Programmable Logic Devices (PLD)

The term PLD is broadly applied to the integrated circuits that have a fixed underlying the term PLD is broadly applied to the integrated circuits that have a fixed underlying (AND or OR) or some complex logic subsysting The term PLD is broadly applied to the integrated circuits that have a fixed underlying set of components such as logic gates (AND or OR) or some complex logic subsystems, but whose interconnections can be tailored by the circuit designer through external programming in an application specific way that makes them general purpose design components. The number of components in PLDs may be very large, so that it spans to range of complexity from MSI to VLSI. Under these PLDs we have Programmable Array logic (PAL). Programmable Logic Array (PLA), Programmable Logic Element (PLE) and range or complexity from M31 to VL31. Office A Programmable Logic Element (PLE) ar Logic (PAL), Programmable Logic Array (PLA), Programmable Logic Element (PLE) ar

In this chapter, we shall develop the design procedure of the combinational circuit using the logic components mainly of the MSI and LSI category. We shall see that the complete design of the circuit with MSI components needs some help of the logic gates of the SSI design of the circuit with MSI components needs some help of the logic gates of the SSI design group also. MSI and LSI components are very much function specific and the design group also. MSI and LSI component integrates more distinct procedure procedure and procedure to the mainly seed to the ma group also. MSI and LSI components are very finder indicated and the design concept needs some new approach. As the MSI and LSI component integrates more digital subsystems in a single chip, the number of chip-count of the circuit and necessary wiring subsystems in a single chip, the number of chip-count of the circuit becomes more reliable and for the interconnections are reduced and hence the circuit becomes more reliable and cost effective

Following is the list of the MSI and LSI components whose functional properties, logic structure and a few applications of each will be considered in this chapter

Multiplexer, Demultiplexer, Magnitude Comparator, Decoder, Decoder Driver, Encoders, Code-Converters, Parity Generator and Checker, Logic Shifter and PLDs.

### MULTIPLEXER

### 8.2.1 Introduction

Multiplexing means transmiting a large number of information units over a small number of channels or lines. The multiplexer is a combinational circuit which serves this purpose. A multiplexer circuit, in general, may have M data inputs and one output line. The selection of input to output transfer path is controlled by set of N select lines. The select lines are also called the address of the inputs. The relationship between these N address lines and the M data input lines is  $M = 2^N$ . Because, using N-bit binary inputs to the select lines we may generate 2<sup>N</sup> address codes and each code addresses one data input line out of M. The multiplexer in short is called MUX. The MUX with M inputs and 1 output is mentioned in the literature as (M  $\times$  1) or as M-to-1 MUX. For example, a MUX with 4 data inputs and 1 output is called  $4 \times 1$  or 4-to-1 MUX. Besides these inputs and output, usually, for all kinds multiplexers at least one input line is available which is known as Enable line. This enable line is either active low or active high type. If the enable input is kept inactive then the multiplexer circuit becomes inactive. Commercially available MUXs usually come with active low enable lines. This means that the multiplexer circuit will be active i.e. will

### COMBINATIONAL LOGIC CIRCUIT IMPLEMENTATION WITH SSI AND MSI ▼ 581

follow its functional behavior if the enable line is made logic low otherwise there will be no variations at the output though the different inputs are selected using select codes

applied to the select inputs. Under disabled condition the output will show either a logic-0 or logic-1 irrespective of the select inputs. Whether the state of the output will be logic-0 or 1 under disabled condition of the muttiplexer depends on the internal circuit design of the multiplexer.

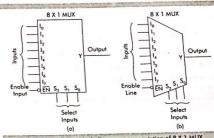

The block diagram for a 8-to-1 MUX is shown in Fig. 8.1. The Fig. 8.1 (a) and (b) are two alternative logic symbols that are used for

the 8-to-1 MUX. In the logic symbol we can see that there are 8 data input lines ( $I_{0}$ ,  $I_{1}$ )  $I_2$ , .....,  $I_2$ ), three select lines  $(S_2, S_1, S_0)$ , one active-low enable line  $(\overline{EN})$  and one output line Y. Out of these 8 data inupts, any one input is selected at a time by the select code for receiving digital data and

Output ) Select Inputs Selected will be same as Input Input S (EN) S S 0  $I_1$ 0 0 0 0 1 I, 0 0 1 1  $I_3$ 0 14 1 0 0 1 Is 0 1 I, 1 0 I6 16 0 1 I, 1 1 I, 0 X None

TABLE 8.1 Functional table of a 8-to-1 MUX

proper select setting the codes to the select inputs  $S_2$ ,  $S_1$ , and  $S_0$ . For example if  $S_2S_1S_0 = 010$  then the  $I_2$  input will be selected for receiving digital data i.e. the binary bit 1 or 0 through the input I<sub>2</sub> will be passed to be output Y and at this time all other input lines  $I_0$ ,  $I_1$ , and  $I_3$  to  $I_7$  will remain deselected i.e. no

for transmission of the data

from the selected input to the

output Y. The selection of the

particular input is done by

digital signals will be able to pass through them to reach the output Y. That is, the selection of input is done one at a time. The function table (TABLE 8.1) explains the complete behavior of a 8-to-1 MUX. For this illustration, the enable input (EN) is assumed to be active-low and under disabled condition (EN=1) the output (Y) is assumed to be low.

From this function table we may write down the logic equation for the output Y in terms of the inputs  $(I_0, I_1, ..., I_7)$  and the select inputs  $(S_2, S_1 \text{ and } S_0)$  and the active-low enable input EN. The logic equation for this 8-to1 MUX using the TABLE 8.1 is

$$Y = (\overline{S}_2 \overline{S}_1 \overline{S}_0 I_0 + \overline{S}_2 \overline{S}_1 S_0 I_1 + \overline{S}_2 S_1 \overline{S}_0 I_2 + \overline{S}_2 S_1 S_0 I_3 + S_2 \overline{S}_1 \overline{S}_0 I_4 + S_2 \overline{S}_1 \overline{S}_0 I_4 + S_2 \overline{S}_1 \overline{S}_0 I_5 - \overline{S}_0 \overline{S}_0 I_5 + \overline{S}_0 \overline{S}_0 \overline{S}_0 I_5 + \overline{S}_0 \overline{S}_0 \overline{S}_0 \overline{S}_0 I_5 + \overline{S}_0 \overline$$

$$= (\sum_{i=1}^{7} m_i I_i) \overline{EN} \qquad .... (8.1)$$

$S_0$  (e.g.  $\overline{S_2S_1S_0} = m_0$ ,  $\overline{S_2S_1S_0} = m_1$ ,  $\overline{S_2S_1S_0} = m_2$  etc),  $I_1$  is the  $I^{th}$ data input line and EN is the active low enable input. In where m, represents ith minterm of select variable S2 S1 and general the logic equation for a MUX with n number of select inputs and active low enable input may be written as

$$Y = (\sum_{n=1}^{2^{n-1}} m_i I_i) \overline{EN}.$$

(8.2)

position of the switch arm to the appropriate input I. This is shown in Fig 8.2. From the above discussions we may view one MUX as a rotary mechanical swtich with select inputs determining the

# Design of 4-to-1 Multiplexer

The Eqn 8.2 is for 2"-to-1 MUX and this equation represents a sum of product form. Therefore, Eqn. 8.2 can be realised using a 2-level AND-OR logic circuit. For a 4-to-1. MUX

enable input.

Output Select Inputs S Enable EN

TABLE 8.2 (a) Function table of a 4-to-1 MUX with active high

collects the outputs of all the analys. s it is easy to show that because the AND gate-2 give the output of AND gate-1. The

# COMBINATION/

input and one output (Y). The ft this table, the logic equation fo

$$Y = (\overline{S_1}\overline{S_0}I_0 + \overline{S_1}S_0I_1 + S_1\overline{S_1})$$

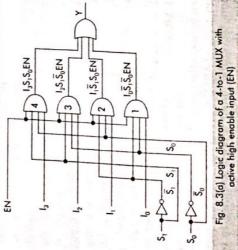

4 rows of the functional table of 8.2(a). Otherwise for EN = 0 th circuit for the Eqn (8.3) is show where S<sub>1</sub> and S<sub>n</sub> are the selec 4 data inputs and EN is the activ enable input is made logic-1 the ignoring of select and data inpu diagram representation is show

From this logic circuit it is s of inverters and one OR gate v AND gates to generate the pri inverters to get  $\overline{S}_1$  and  $\overline{S}_0$  from 4-input OR gate to get the final and one enable line, we need 2n

Fig. 8.2 Multiplexer as

a rotary switch

5, 5, 5,

position

Switch

From the circuit of Fig. 8.3 ( = 0, So=0 and EN=1 the outputs

Fig. 8.3(c) Logic circuit of a 4-toactive low enable inpu

there will be 4 data inputs, 1 output and optionally there may be one enable input. The enable input may be active low or active high type. Also, some MUXs give output polarity inverse of the selected input. Let us design a 4-to-1 MUX with active high enable (EN)  $S_1 S_0 = 10$  and EN = 1, the output Y is  $I_2$  as the AND gate-3 gives an output  $I_2$  with all other AND-gate outputs at logic-0; for  $S_1 S_0 = 11$  and EN = 1, the output Y is  $I_3$  as the

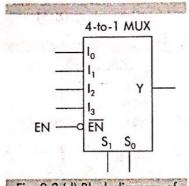

Fig. 8.3 (d) Block diagram of 4-to-1 MUX with active low enable input.

AND gate-4 gives an output  $I_3$  with all other AND gate outputs at logic-0. But, for EN = 0 all the AND gates will give logic 0 output irrespective of the different select inputs on  $S_3$ ,  $S_2$  and  $S_0$ . This leads to the logic-0 output at Y for all times so long as EN is low. This is indicated in the last row of the TABLE 8.2(a).

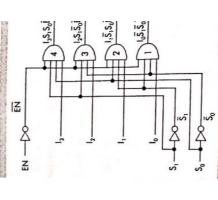

The logic circuit of a 4-to-1 MUX with active low enable input is shown in Fig. 8.3 (c) and its logic symbol is shown in Fig. 8.3 (d). The function table of the circuit in Fig. 8.3 (c) is shown in TABLE 8.2 (b).

The output Y of this MUX can be written from the TABLE 8.2(b) as  $Y = (I_0 \overline{S}_1 \overline{S}_0 + I_1 \overline{S}_1 S_0 + I_2 S_1 \overline{S}_0 + I_3 S_1 S_0) \overline{EN}$ .

### 8.2.3 Commercially Available 4-to-1 Multiplexer IC chips

TABLE 8.3 shows a list of currently available commercial TTL 4 to-1 MUX IC chips with their brief description. From the table it may be seen that each IC chip is dual 4-to-1 MUX which means that each chip contains two identical units of 4-to-1 MUX inside. The two units are not completely independent because their select inputs (S<sub>1</sub> and S<sub>0</sub>) are common. From the last column of this table it is evident that the MUXs may produce three types of outputs (i) Same as inputs i.e. polarity of the output is same as that of the data inputs (ii) Inverse of the inputs; i.e. the polarity of the output is complement of the data inputs (iii) same as that of the cases (i) and (ii) but the output is tristated. For the third category of multiplexers (IC 74253 and IC 74353) there is a control input called "output control" line which when made logic high the output goes into a high impedance state otherwise the IC 74253 and 74353 are similar to 74153 and 74352 respectively. The function tables of 74153, 74352, 74253, and 74353 are shown in TABLE 8.4 (a), (b), (c) and (d). The MUX with tristated outputs are usually used in a bus oriented circuits. For all these MUXs the enable inputs and the tristate-control inputs are active low. Brief description and the logic circuit of the different 4-to-1 MUXs are given below.

| TTL IC Chip<br>number | No. of<br>Pins | Technology<br>used | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Polarity of output    |  |

|-----------------------|----------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| 74 153                | 16             | Std TTL, L, LS, S, | Dual 4-to-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Same as Input         |  |

|                       | mar string     | HC                 | MUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | and the second of     |  |

| 74 352                | 16             | LS, S, ALS, AS, HC |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | complement of         |  |

|                       |                |                    | -M-2777                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | inputs                |  |

| 74 253                | 16             | LS, S, ALS, AS, HC | The state of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Same as input but the |  |

|                       |                |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | output tristated      |  |

| 74 353                | 16             | LS, ALS, AS, HC    | or Marian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | complemented but the  |  |

| recovery 5            |                |                    | The control of the co | output tristated      |  |

TABLE 8.3 Commercially available 4-to-1 multiplexer IC chips

Control (2G)

Fig. 8.5 (a) Logic circuit of 74253.

Fig. 8.5 (b) Block diagram of 74253

# Commercially Available 8-to-1 Multiplexer IC Chips

| TTL IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No. of<br>Pins | Technology<br>Used | Functional description | Polarity of                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|------------------------|------------------------------------------------|

| 74151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16             | LS, S ALS, AS, HC  |                        | Two outputs. Polarity                          |

| The chartee of the Shares that the chartest of | ALSOPS I       | ewit szakó a poi   | Lossent a el que       | one is same as input<br>and the other is inver |

| 74152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16             | LS, HC             | e testated NOR gate    | of inputs. One output, inverse                 |

| 74251                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16             | LS, S, ALS, HC     | to ex qual time to me  | Two tristated output one is same as input at   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | For well       | nd has in Fig.     | 3 / 1 still in cast to | the other is inverse input.                    |

8.3 C

# Cascading of Multiplexers

The input capacity of multiplexer can be increased by cascading several multiplexers. By m-to-1 MUX for outputting data. All the multiplexers used in this method are kept always MUXs. (ii) Using m number of n-to-1 MUX for inputting data from (mxn) sources and one at the output stage needs  ${f m}$  inputs because it collects the  ${f m}$  outputs from  ${f m}$  numbers of another by using some input logic circuit called decoding logic circuit. The OR gate used (mxn) sources and one m-input OR-gate for outputting data. The select lines of all the m numbers multiplexers are made common and the multiplexers are enabled one after cascading m numbers of n-to-1 MUXs we can have a multiplexing action equivalent to (mxn)-to-1 MUX. Thus, the input capacity is increased from n to (mxn). This cascading can be done in two ways- (i) Using m numbers of n-to-1 MUXs for inputting data from enabled. Following examples will explain the two modes of connections :

Example 2

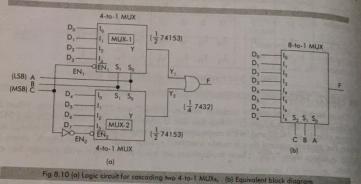

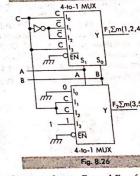

Cascade two 4-to-1 MUX IC chips (IC 74153) to make an equivalent 8-to-1 MUX.

Solution

Method-I

$S_1$  and  $S_0$  of the MUX-1 are connected to the select lines  $S_1$  and  $S_0$  of MUX-2 respectively The interconnections of the two 4-to-1 MUXs is shown in Fig. 8.10 (a). The select lines

i.e. the two MUXs have common select lines. The active low enable inputs of the MUXs are connected by an inverter as shown in the Fig. 8.10 (a) so that the MUX-1 remains enabled by an inverter as shown in the Fig. 8.10 (a) so that the MUX-1 remains enabled b<sub>1</sub> or D<sub>2</sub> or D<sub>3</sub> depending on whether BA = 00 or 01 or 10 or 11. Under this condition that MUX-2 remains in the disabled condition because EN<sub>2</sub>=1 as C = 0 and hence Y<sub>2</sub> = 0. Hence the output of the OR gate follows Y<sub>1</sub>.

Similarly, when C = 1 the MUX-2 is enabled as  $EN_2 = 0$  and MUX-1 goes to the disabled condition as  $EN_1 = 1$ . For this situation  $Y_1$  is always at logic-0 and the output  $Y_2$  of MUX-2 follows either  $D_1$  or  $D_2$  or  $D_3$ .

MUX-2 follows either D<sub>4</sub> or D<sub>5</sub> or D<sub>6</sub> or D<sub>7</sub> for the input BA varying from 00 to 11. For this reason the output F of the OR gate follows Y<sub>2</sub>. The functional table of the circuit of Fig. 8.10 (a) is shown in TABLE 8.11. Concentrating on the select inputs C, B and A and the output F of this table we may conclude that the two 4-to-1 MUXs cascaded as in Fig. 8.10 (a) is equivalent to one 8-to-1 MUX. The block diagram of the equivalent MUX is shown in Fig. 8.10 (b). For this cascaded multiplexer circuit the input C, B and A become the select inputs where C is MSB and A is the LSB.

|   | Input |   |                 |                 |                | Ou             | tput            |

|---|-------|---|-----------------|-----------------|----------------|----------------|-----------------|

| C | В     | A | EN <sub>1</sub> | EN <sub>2</sub> | Y              | Y <sub>2</sub> | $F = Y_1 + Y_2$ |

| 0 | 0     | 0 | 0               | 1               | Do             | 0              | D <sub>0</sub>  |

| 0 | 0     | 1 | 0               | 1               | Di             | 0              | D <sub>1</sub>  |

| 0 | 1     | 0 | 0               | 1               | D <sub>2</sub> | 0              | D,              |

| 0 | 1     | 1 | 0               | 1               | D <sub>3</sub> | 0              | D <sub>3</sub>  |

| 1 | 0     | 0 | 1               | 0               | 0              | D <sub>4</sub> | D <sub>4</sub>  |

| 1 | 0     | 1 | 1               | 0               | 0              | D <sub>5</sub> | D <sub>5</sub>  |

| 1 | 1     | 0 | 1               | 0               | 0              | D <sub>6</sub> | D <sub>6</sub>  |

| 1 | 1     | 1 | 1               | 0               | 0              | D <sub>7</sub> | D <sub>7</sub>  |

TABLE 8.11 Function table of the circuit of Fig. 8.10

COMBINATIONAL LOGIC CIRCUIT IMPLEMENTATION WITH SSI AND MSI ▼ 599

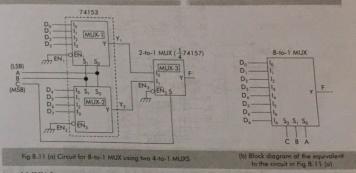

### Method-II

The interconnection of the MUXs for this method is shown in Fig. 8.11 (a).

This logic circuit is constructed using only MUXs and all the MUXs are enabled permanently by connecting their enable inputs to ground. The select lines S and  $S_0$  of MUX-

1 and MUX-2 are common. So, for any input combination to B and A, data inputs of MUX-1 and MUX-2 of same order are selected and the data are available at the outputs Y<sub>1</sub> and

Inputs Outputs C B F 0 0 0 D4 Do 0 D, D<sub>5</sub> D, 0 D, De D, 0 D. D.  $D_3$ Do D<sub>4</sub> D4 0 D, D<sub>5</sub> 0 D, D, D D3 D. D7

TABLE 8.12 Functional table for the circuit in Fig. 8.11 (a).

$Y_2$ . For example, if BA = 10 then the input  $I_2$  of both MUX-1 and MUX-2 will be selected for receiving data  $D_2$  and  $D_6$  but for C=1 the select input S of MUX-3 is 1 and hence  $I_1$  input of MUX-3 is selected. Hence, for C=1 the  $Y_2$  output of MUX-2 will be selected and the final output F will follow  $D_6$ . If C=0 then the final output will be  $F=Y_1=D_2$  because for C=0 the select input S of MUX3 is 0 and hence MUX3 selects only its  $I_0$  input. The function table (TABLE 8.12) shows the final output F for different combinations of C, B and A. If we consider the input columns and the column for output F then we may say that the circuit of Fig. 8.11(a) behaves as an  $I_2$  to this circuit is shown in the Fig. 8.11(b).

it is seen that all the enable lines of the MUXs have been used and so there is no enal input left for controlling the equivalent 8-to-1 MUXs. To have the enable action in Fig. 8 (a) we may connect the enable inputs  $\mathrm{EN}_1$ ,  $\mathrm{EN}_2$  and  $\mathrm{EN}_3$  of the MUXs together instead of connecting them to the ground permanently. The common point can be used as an action of the second of the seco

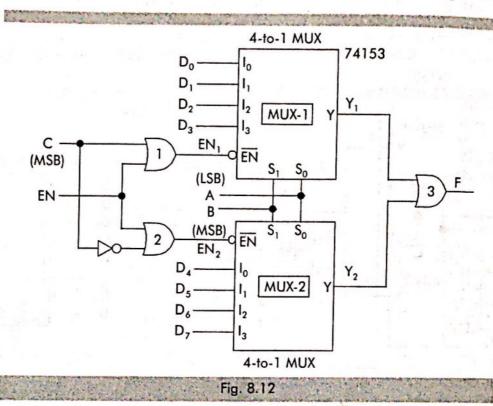

low enable input. For the circuit of Fig. 8.10 (a) we may use two 2-input OR gate at the enable input of the MUX-1 and MUX-2 as shown in Fig. 8.12. In this circuit if the input EN is 0 then the logic state of the line C will reach the enable of input of MUX-1 and the

inverse of C i.e.  $\overline{C}$  will reach the enable input of MUX-2. For this reason for C=0, the MUX = 1 will be enabled and the MUX-2 will be disabled. But for C=1 and EN=0 the MUX-2 will be enabled and MUX-1 will go into disabled condition. When EN=1 the output of the OR gates 1 and 2 will always be 1 and the two MUXs will be in the disabled condition producing  $Y_1=Y_2=0$  and hence F=0.

### Example 3

- (i) Design a 16-to-1 MUX using all 4-to-1 MUXs.

- (ii) Design a 16-to-1 MUX using 8-to-1 and other suitable MUX.

- (iii) Design a 16-to-1 MUX using all 8-to-1 MUXs.

- (iv) Design a 16-to-1 MUX using two 8-to-1 MUXs and NAND gate.

### Multiplexer as Logic Function Generator

It is already known to us that the output equation (Equn. 8.1 as an example) of a multiplexer can be expressed as cannonical SOP form i.e. as a sum of a fixed number of minterms. The number of minterms depends on the number of select inputs. For example, if there are N select inputs then there will be  $2^N$  number of minterms. Each minterm contains (N+1) number of literals. Out of these (N+1) literals the N literals come from the select variables and one literal is due to the input data variable. For example, for a 4-to-1 MUX with select variables  $S_1$  and  $S_0$  and the input data variables  $D_0$ ,  $D_1$ ,  $D_2$  and  $D_3$  the output equation of this MUX is

$$F = \overline{S}_1 \overline{S}_0 D_0 + \overline{S}_1 S_0 D_1 + S_1 \overline{S}_0 D_2 + S_1 S_0 D_3.$$

The enable input is not considered in this equation.

To realise any function using a MUX we have to express the function in a standard canonical form and then we have to compare each minterm with the terms of the output equation of the MUX to get the idea for using the function variables as the select and the data variable of the given MUX. The absent minterms for the function can be realised by applying logic-0 to the data input lines. Following are some procedures which can be used to realise a logic function using multiplexers

(i) Algebraic Approach, (ii) Using Truth Table, (iii) Using K-Map, (iv) Using Implementation Table, (v) Using MUX Trees.

Digital—77

### 8.4.2 Using Truth Table

The circuit using multiplexers can also be realised starting from the truth table of the given function. In this method the rows of the truth table of n-variable function are partitioned in such a way that any m number of variables (m < n) in each partition have the same logic values After such partitioning, one should find out the functional dependance of the output F on the remaining variables (n - m) of each partition. These functional dependance from each partition gives the multiplexer inputs and the m variables whose logic values do not change in a partition become the select inputs of the multiplexer.

Digital—78

Let us consider the truth table [TABLE 8.17(a)] of 3 variables A, B, C, This table is partitioned with respect to two variables, A and B such that in partition-I, AB = 00; in partition-III, AB = 01; in partition-III, AB = 10 and in partition-IV, AB = 11. The partitioning is shown in TABLE 8.17(b). It is seen from the partition-I that for AB = 00, the output is same as C Therefore, we may write that F = C so long as A = B = 0. Similarly, when AB = 0 the output E = C and when AB = 11 the AB = 01 the output  $F = \overline{C}$ ; when AB = 10, the output  $F = \overline{C}$  and when AB = 11 the output F = C. Thus, the TABLE 8.17(b) may be described in a more compact form as shown is TABLE 8.17 (c).

| 0.007 | Inp | ut | Output |

|-------|-----|----|--------|

| A     | В   | С  | F      |

| 0     | 0   | 0  | 0      |

| 0     | 0   | 1  | 1      |

| 0     | 1   | 0  | 1      |

| 0     | 1   | 1  | 0      |

| 1     | 0   | 0  | 1      |

| . 1   | 0   | 1  | 0      |

| 1     | 1   | 0  | 0      |

| 1     | 1   | 1  | 1      |

|               |   | I | npu | Output |   |

|---------------|---|---|-----|--------|---|

|               | 1 | A | В   | С      | F |

|               | , | 0 | 0   | 0      | 0 |

| Partition-I   | 1 | 0 | 0   | 1      | 1 |

|               | { | 0 | 1   | 0      | 1 |

| Partition-II  |   | 0 | 1   | 1      | 0 |

|               | 7 | 1 | 0   | 0      | 1 |

| Partition-III | 1 | 1 | 0   | 1      | 0 |

|               | , | 1 | 1   | 0      | 0 |

| Partition-IV  | 1 | 1 | 1   | 1      | 1 |

|   | A | В | F                    |

|---|---|---|----------------------|

| I | 0 | 0 | C(=I <sub>0</sub> )  |

|   | 0 | 1 | $\overline{C}(=I_1)$ |

| 1 | 1 | 0 | C(=I2)               |

|   | 1 | 1 | C(=I <sub>3</sub> )  |

TABLE 8.17 (a)

TABLE 8.17 (b)

TABLE 8.17 (c)

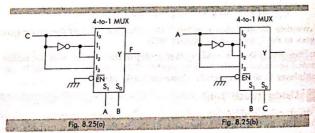

The last column of this compact table describes the inputs to the 4-to-1 multiplexer with A and B as the select inputs  $(S_1, S_0)$ . The inputs  $I_0$ ,  $I_1$ ,  $I_2$  and  $I_3$  have been indicated in this table. The connections of C, A and B to the 4-to-1 MUX is shown in Fig. 8.25(a).

If we decide to use B and C as the select variables (i.e.  $S_1 = B$ ,  $S_0 = C$ ) then we have to rearrange the given truth table so that the rows of the 1st, 2nd, 3rd and 4th partition, have the values BC = 00, 01, 10 and 11 respectively. The rearranged truth table is shown in TABLE 8.17(d). The compact table and the corresponding circuit with select inputs

### Sombinational logic circuit implementation with SSI and MSI $\blacktriangledown$ 619

$S_1$  = B and  $S_0$  = C of a 4-to-1 MUX is shown in TABLE 8.17(e) and Fig. 8.25(b) respectively. Similarly, we might have used A and C as the select variables.

|               | Inpu  | Output |   |  |

|---------------|-------|--------|---|--|

|               | BC    | A      | F |  |

|               | , 0 0 | 0      | 0 |  |

| Partition-I   | 100   | 1      | 1 |  |

| 7             | , 0 1 | 0      | 1 |  |

| Partition-II  | 101   | 1      | 0 |  |

|               | , 1 0 | 0      | 1 |  |

| Partition-III | 1 1 0 | 1      | 0 |  |

|               | , 1 1 | 0      | 0 |  |

| Partition-IV  | 1 1 1 | 1      | 1 |  |

| TABLE | 8.17 | (d) |

|-------|------|-----|

|       |      |     |

| В | C | F                     |

|---|---|-----------------------|

| 0 | 0 | $A(=I_0)$             |

| 0 | 1 | $\overline{A} (=I_1)$ |

| 1 | 0 | $\overline{A} (=I_2)$ |

| 1 | 1 | $A(=I_3)$             |

TABLE 8.17 (e)

Implement circuit  $F_1(A, B, C) = \sum m(1, 2, 4, 7)$  and  $F_2(A, B, C) = \sum m(3, 5, 6, 7)$  using 4-to-1 multiplexers and inverter. Use truth table approach.

Solution The truth table of this example is shown in the TABLE 8.18(a). The table partitioned with respect to the two variables A and B. The compact truth table is shown

| THE STATE OF  |   | L | npu | t | Output         |                |  |

|---------------|---|---|-----|---|----------------|----------------|--|

|               |   | A | В   | C | F <sub>1</sub> | F <sub>2</sub> |  |

|               | - | 0 | 0   | 0 | 0              | 0              |  |

| Partition-I   | 1 | 0 | 0   | 1 | 1              | 0              |  |

|               | - | 0 | 1   | 0 | 1              | 0              |  |

| Partition-II  | 1 | 0 | 1   | 1 | 0              | 1              |  |

| D. CC III     | 1 | 1 | 0   | 0 | 1              | 0              |  |

| Partition-III | 1 | 1 | 0   | 1 | 0              | 1              |  |

|               | 1 | 1 | 1   | 0 | 0              | 1              |  |

| Partition-IV  | 1 | 1 | 1   | 1 | 1              | 1              |  |

TABLE 8.18 (a)

| A | B | F <sub>1</sub> .     | F <sub>2</sub>      |

|---|---|----------------------|---------------------|

| 0 | 0 | $C(=I_0)$            | $0(=I_0)$           |

| 0 | 1 | $\overline{C}(=I_1)$ | C(=I <sub>1</sub> ) |

| 1 | 0 | $\overline{C}(=I_2)$ | C(=I <sub>2</sub> ) |

| 1 | 1 | $C(=I_3)$            | 1(=I <sub>3</sub> ) |

TABLE 8.18 (b)

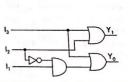

in TABLE 8.18 (b). The two columns  $F_1$  and  $F_2$  of 8.18(b) are used as the inputs I<sub>0</sub>, I<sub>1</sub>, I<sub>2</sub> and I<sub>3</sub> to two s 4-to-1 MUXs with A and B as the common select for both. The implemented circuit is shown in F

Implement the function  $F(A, B, C, D) = \sum m(0, 2, 4, 6, 8, 10, 14)$  using one 4-to-1 MUX and necessary logic gates.

Solution The truth table for this example is shown in TABLE 8.19 (a). Since we have

to design the circuit using 4-to-1 MUX which needs two select inputs, therefore, this table is partitioned with respect to two variables A and B assuming that these two variables are to be used as the select inputs S<sub>1</sub> and S<sub>0</sub> respectively. This choice of the two select variables is arbitrary. Any two variables out of A, B, C and D could have been used for the select variables. For the partition-I, partition-II, partition-III, and partition-IV the values of the variables A and B are 00, 01, 10 and 11 respectively. The output F as a function of the remaining two variables C and D of this truth table is shown in the TABLE 8.19 (b). This is the compact truth table of TABLE 8.19 (a). The expression for F(C, D) for the 4 inputs to the 4-to-1multiplexer can easily be obtained using K-maps drawn separately for each partition. For this problem we may use four 2-variable K-maps, one for each partition where the map variables will be C and D. For

| AND THE PARTY | 100 |   | Output |    |   |       |

|---------------|-----|---|--------|----|---|-------|

|               | 53  | A | В      | C  | D | F     |

|               | 1   | 0 | 0      | 0  | 0 | 1     |

| Partition-I   |     | 0 | 0      | 0  | 1 | 0     |

|               | 11  | 0 | 0      | 1  | 0 | 1     |

|               | 1   | 0 | 0      | 1  | 1 | 0     |

|               | 1   | 0 | 1      | 0  | 0 | 1     |

| Partition-II  |     | 0 | 1      | 0  | 1 | 0     |

|               | 11  | 0 | 1      | 1  | 0 | 1     |

|               | 1   | 0 | 1      | 1  | 1 | 0     |

|               | 1   | 1 | 0      | 0  | 0 | 1     |

| eriolat       |     | 1 | 0      | 0  | 1 | 0     |

| Partition-III | 1   | 1 | 0      | 1  | 0 | 1,7,7 |

|               | l   | 1 | 0      | 1. | 1 | 0     |

|               | 1   | 1 | 1      | 0  | 0 | 0     |

|               |     | 1 | 1      | 0  | 1 | 0     |

| Partition-IV  | 1   | 1 | 1      | 1  | 0 | 1     |

|               | (   | 1 | 1      | 1  | 1 | 0     |

TABLE 8.19 (a)

simple cases the function F(C, D) can be obtained by inspection of the columns of C and D. For example, in this problem for the three partitions I, II and III we can directly find

that the output function F is inverse of the column D so we may write  $F = \overline{D}$  but for

☐ COMBINATIONAL LOGIC CIRCUIT IMPLEMENTATION WITH SSI AND MSI  $\blacktriangledown$  621

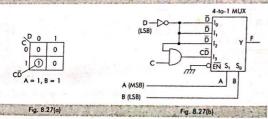

partition-IV we may use a K-map for F using C and D as the map variables, to get the functional dependance of F on C and D (though it is not very difficult to obtain the expression F(C, D) = CD by observation). B F (C,D) The K-map for this partition is shown in FIg. 8.27(a) which gives  $F(C, D) = C\overline{D}$ . The compact table TABLE 8.19 (b) gives the four  $\widetilde{D}$  (= $I_0$ ) 0 multiplexer inputs  $I_0$ ,  $I_1$ ,  $I_2$  and  $I_3$  for different select inputs AB = 00, 01, 10 and 11. The circuit for this example is shown in  $\overline{D}(=I_1)$ 1 0  $\overline{D}$  (= $I_2$ ) 0 1

Fig. 8.27(b).

1 TABLE 8.19 (b)

$C\overline{D}(=I_3)$

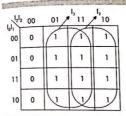

### 3.4.3 Using Karnaugh Map

If the functional behavior of a circuit is described using a K-map then the implementation of the circuit using a multiplexer can easily be done starting from this map. In the n-variable K-map, if we decide to use m number of variables as the select variables then the groupings of the remaining (n-m) variables gives us the multiplexer inputs  $I_0$ . Let us consider the following illustrations to explain the procedure for obtaining the multiplexer inputs.

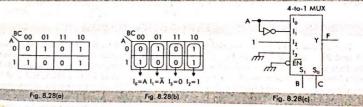

Let us consider a K-map of a 3-variable function F(A, B, C) as plotted in Fig. 8.28(a). Out of these 3 map variables A, B and C we may use any two variables as the select inputs of a 4-to-1 multiplexer. The easiest way is to choose B and C as the select variables since the columns of K-map in Fig 8.28(a) are already coded according to the four 2-bit binary select codes of a 4-to-1 MUX, i.e. BC = 00, 01, 10, 11.

The K-map is divided into four groups as shown in Fig. 8.28(b) where in each group the logic values of B and C do not change but that of the variable A changes. For the first column of the K-map, BC = 00 and the function F in this group is

> F = 0when A = 0 and BC = 00when A = 1 and BC = 00F = 1

Therefore, we may write F = A when BC = 00.

Therefore, it may be said that if B and C are used as the select inputs of a 4-to-1 MUX then the input  $I_0$  of this MUX is to be connected to A to satisfy F = A with BC = 00.

001, 010, 011, 100, 101, 110 and 111 are shown in Fig. 8.28(o) and also the inputs  $I_0$  to  $I_7$  are indicated in general. For our specific example we may follow the grouping techniques of Fig. 8.28(o) to get  $I_0 = 1$ ,  $I_1 = 0$ ,  $I_2 = 1$ ,  $I_3 = D$ ,  $I_4 = D$ ,  $I_5 = \overline{D}$ ,  $I_6 = 0$  and  $I_7 = 1$  from the Fig. 8.28(p). The circuit with these eight inputs is shown in Fig. 8.28(q).

### 8.4.4 Using Implementation Table

This is a tabular method for finding the inputs of the multiplexer when the minterm numbers for the given function to be implemented are known to us. The implementation table has two rows and M number of columns where the number M is half of the maximum number of minterms possible with N-variable function. For N-variable function the

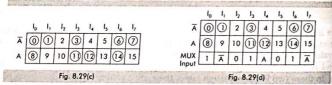

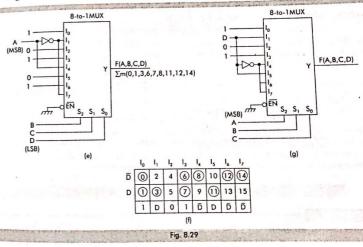

maximum number of minterms is  $2^N$ . So, the value of M is  $\frac{2^N}{2} = 2^{N-1}$ . If we check  $2^N$  minterms of any Boolean function having N variables then we find that any variable appears in the uncomplemented form in exactly one half of the total number of minterms, while other half contains complemented form of that variable. In an implementation table the top row is labeled with the complement of a variable (i.e. say  $\overline{A}$ ). of the function F(A, B, C, D) and the bottom row is labeled with the true form of the same variable (i.e. A) of the function. The top row lists all minterms which are associated with the variable in complemented form and the second row lists all minterms with that variable in the uncomplemented form. Usually, either the most significant or the least significant variable is used for labelling the rows. For example, Fig.8.29(a) and Fig.8.29(b) show the structure

| 1 | 1, | l <sub>2</sub> | l <sub>3</sub> | l <sub>a</sub> | 15 | 16 | 1, |   | Io | I <sub>1</sub> | 12 | l <sub>3</sub> | 14 | 15 | 16 | 17 |

|---|----|----------------|----------------|----------------|----|----|----|---|----|----------------|----|----------------|----|----|----|----|

| 0 | 1  | 2              | 3              | 4              | 5  | 6  | 7  | D | 0  | 2              | 4  | 6              | 8  | 10 | 12 | 14 |

|   | -  | 10             | 11             | 12             | 13 | 14 | 15 | D | 1  | 3              | 5  | 7              | 9  | 11 | 13 | 15 |

of the implementation table for a four variable function F (A, B, C, D). In Fig 8.29(a) the most significant variable A is used for row heading and the corresponding decimal equivalent number of the minterms are inserted in the boxes which are associated with  $\overline{A}$  and A. Similarly, in Fig.8.29(b) the least significant variable D is used for heading the rows. In these two implementation tables there are 8 columns and each column is headed by the multiplexer inputs  $I_0$ ,  $I_1$ ,  $I_2$ , ....,  $I_7$ . As there are 8 inputs so we need an 8-to-1 MUX to realise the function F (A, B, C, D). In general, for an N-variable function we need a MUX having (N – 1) select inputs and  $2^{N-1}$  data input lines.

Clearly, the entries in each column in Fig. 8.29(a) are determined by the bit combination of the variables A, B, C and D. For example, in the column  $I_3$  there are two numbers,  $3(\equiv \overline{A}\,\overline{B}CD)$  and  $11(\equiv A\overline{B}CD)$  with row heading  $\overline{A}$  and A respectively. The last three literals  $\overline{B}$ , C and D constitutes the select code of MUX input  $I_3$ . For the Fig.8.29(a), the numbers for the two boxes under any column  $I_i$  can be determined by writing the rowheading literal corresponding to that row in the most significant position followed by the

select code of  $I_i$ . Similarly, in case of Fig.8.29(b) the row-heading variable are written are  $\overline{D}$  or D) after the select code of select code of  $I_i$ . Similarly, in case of Fig. 0.2(c),  $\overline{D}$  or  $\overline{D}$  or  $\overline{D}$  after the select code of  $I_i$  the least significant variable (in this case they are  $\overline{D}$  or  $\overline{D}$ ) after the select code of  $I_i$  to the least significant variable (in this case usey are 50 to 2), the the numbers under the column I<sub>i</sub>. In this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers under the column I<sub>i</sub>. In this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers of the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers of the numbers under the column I<sub>i</sub> in this case the select codes are obtained using the numbers of the the numbers under the column 1, in this case the decimal number 12 and 13 are write variables A, B, C For example, in Fig. 8.29(b) the decimal number 12 and 13 are write column of L because select code to select Mus. variables A, B, C For example, in the column of  $I_b$  because select code to select MUX in the top and bottom row under the column of  $I_b$  because select code to select MUX into of  $I_b$  using select variables A, B and C is  $AB\overline{C}$  and the row heading literal for the top of  $I_b$  using select variables A, B and C is  $AB\overline{C}$  and the row heading literal for the top  $I_b$ . of  $\underline{I}_6$  using select variables A, B and C is ADC and an experiment of  $\underline{I}_6$  using select variables A, B and C is ADC and an experiment of  $\underline{I}_6$  using select variables A, B and C is ADC and an experiment of  $\underline{I}_6$  using select variables A, B and C is ADC and an experiment of  $\underline{I}_6$  using select variables A, B and C is ADC and an experiment of  $\underline{I}_6$  using select variables A, B and C is ADC and an experiment of  $\underline{I}_6$  using select variables A, B and C is ADC and an experiment of  $\underline{I}_6$  using select variables A, B and C is ADC and an experiment of  $\underline{I}_6$  using select variables A, B and C is ADC and an experiment of  $\underline{I}_6$  using select variables A, B and C is ADC a in D and for the bottom row it is D. Hele D but the land of the bottom for the bottom for the bottom boxes under I<sub>6</sub> mean the decimal number.  $(AB\overline{C})\overline{D} = 12$  and  $(AB\overline{C})D = 13$ .

Fig. 8.29(a) and Fig. 8.29(b) show the boxes for the 16 minterms of a 4-variable function The numbers 0 to 15 within the boxes are the decimal equivalent numbers of the minterms of a 4-variable function. The variable A and D are the most significant variable in Fig. 8.29(a) and least significant variable in Fig. 8.29(b) respectively. Therefore, there in Fig. 8.29(a) and least significant variables in Fig. 8.29(a) and least significant variables. But all the 16 minterms may be a difference in numbering of the boxes in the two tables. But all the 16 minterms may be be present in the given function. The minterms which are actually present in the function are circled in the implementation table.

Thus, the decimal number of the table indicates the decimal equivalent number of the minterm of the function.

Let us now consider an example of a function F (A, B, C, D) =  $\sum m(0, 1, 3, 6, 7, 8, 1)$ 12, 14). To implement this function with MUX taking the help of an implementation table we consider the format of the implementation table as shown in Fig. 8.29(a) in which the minterms which are actually present in the function F are marked with circle. The table after circling the present minterm is shown in Fig. 8.29(c). Let us now develop the following rules to determine the values of the MUX inputs  $I_0$ , ....,  $I_7$  directly from the table simply from the observation of the circled minterms in a column.

The given function F (A, B, C, D) =  $\sum m(0, 1, 3, 6, 7, 8, 11, 12, 14)$  is written as

$$= \overline{A} \, \overline{B} \, \overline{C} \, \overline{D} + \overline{A} \, \overline{B} \, \overline{C} \, D + \overline{A} \, \overline{B} \, \overline{C} \, D + \overline{A} \, \overline{B} \, \overline{C} \, \overline{D} + \overline{A} \, \overline{C}$$

$$= (\overline{A} + A) (\overline{B} \overline{C} \overline{D}) + \overline{A} (\overline{B} \overline{C} D) + (\overline{A} + A) (\overline{B} CD) + A (\overline{B} \overline{C} \overline{D}) + (\overline{A} + A) (\overline{B} C\overline{D}) + \overline{A} (\overline{B} CD)$$

$$+ \overline{A} (\overline{B} CD)$$

$$=1.(\overline{B}\ \overline{C}\ \overline{D})+\overline{A}.(\overline{B}\ \overline{C}\ D)+1.(\overline{B}\ CD)+A.(B\overline{C}\ \overline{D})+1.(BC\overline{D})+\overline{A}.(BCD).$$

### ■ COMBINATIONAL LOGIC CIRCUIT IMPLEMENTATION WITH SSI AND MSI $\blacktriangledown$ 627

Comparing this with multiplexer input equation of an 8-to-1 MUX with select inputs  $S_2 = B$ ,  $S_1 = C$  and  $S_0 = D$  we get

$I_0=1$ ,  $I_1=\overline{A}$ ,  $I_2=0$ ,  $I_3=1$ ,  $I_4=A$ ,  $I_5=0$ ,  $I_6=1$ ,  $I_7=\overline{A}$ . From this result we may develop

Rule 1: If two circled minterms of a F(A, B, C, D) in an implementation table are present the following rules in a column I, then the input I, of the 8-to-1 MUX will be 1 if B, C and D are the select in a column  $I_i$  then the input  $I_i$  of the 6-to-1 MoX will be 1 it 8, variables of the MUX. In this example, we have  $I_0 = I_3 = I_6 = 1$ .

Rule 2: If one circled minterm is present in a column  $I_i$  and in a row with row heading  $\overline{A}$  then the input I<sub>i</sub> of the 8-to-1 MUX will be  $\overline{A}$  if B, C and D are the select variables of the MUX. For example, in this illustration  $I_1 = I_7 = \overline{A}$ .

**Rule 3:** If one circled minterm is present in a column  $I_i$  and in a row with rowheading A then the input  $I_i$  of the 8-to-1 MUX will be A if B, C and D are the select variables of

the multiplexer. In this example,  $I_4 = A$ . Rule 4: If no circled minterm are present in a column I, then the input I, of 8-to-1 MUX will be equal to 0. In this example,  $I_2 = I_5 = 0$ .

The implemented circuit for the function  $F = \sum m(0, 1, 3, 6, 7, 8, 11, 12, 14)$  is shown in Fig. 8.29(e).

In the above illustration the most significant variable A of F (A, B, C, D) and its complement A have been used for heading the two rows of this table and B, C, and D have

### 628 ▼ DIGITAL CIRCUITS

been used as the select variables. If the least significant variable D of the function F(A, C, D) and its complement are used for labelling the rows and A, B, and C as the set variable, then the format of the table in Fig.8.29(b) will be the starting table. By circling a minterms present in the function and applying the 4 rules as stated we can obtain a multiplexer's inputs and the required circuit. These are shown in Fig.8.29(f) and Fig.8.29(f) and Fig.8.29(f) are started to the started of the s

This implementation table has the advantage over the algebraic and K-map methas it gives us a more systemetic procedure to implement a Boolean function us multiplexer. In fact when the number of variables of the function increases then simplementation method becomes more useful.

But, it is not an efficient procedure because using this method it is possible to impleme a function of N variables with MUX having  $2^{N-1}$  inputs rather than with a MUX was samller number of inputs. Following are some examples for using Implementation tables.

### Example 15

Implement the function  $F(A, B, C, D) = \sum_{m} m(0, 2, 3, 4, 8, 10, 14)$  using MUX and other necessary logic gates. Use implementation table for the design.

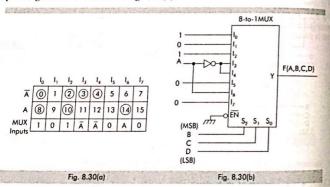

**Solution** This 4-variable function needs one 8-to-1 MUX. Choose  $\overline{A}$ , and A for labeling the rows of the Implementation table and B, C and D as select variables of an 8-to-1 MUX. The implementation table in Fig. 8.30(a) shows the inputs of the 8-to-1 MUX and  $\frac{1}{100}$  corresponding circuit is shown in Fig. 8.30(b).

### Example 16

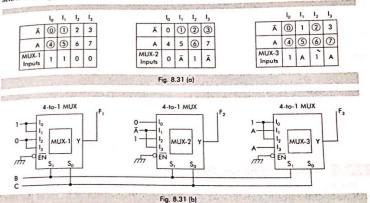

Implement a circuit having three outputs  $F_1$ ,  $F_2$  and  $F_3$  using all 4-to-1 MUXs. The three outputs are  $F_1(A, B, C) = \sum m(0, 1, 4, 5)$ ,  $F_2(A, B, C) = \sum m(1, 2, 3, 6)$  and  $F_3(A, B, C) = \sum m(0, 2, 4, 5, 6, 7)$ . Use implementation table and assume that the complement of the most significant variable (A) is available.

### COMBINATIONAL LOGIC CIRCUIT IMPLEMENTATION WITH SSI AND MSI ▼ 629

Solution For this problem we need three separate Implementation tables which are shown in Fig.8.31(a). Variable A is the row heading variable. The variables, B and C are

used as the select variables for all the 4-to-1 multiplexers. The data inputs of the MUXs are determined from these implementation tables and the corresponding circuit is shown in Fig. 8.31(b).

### Example 17

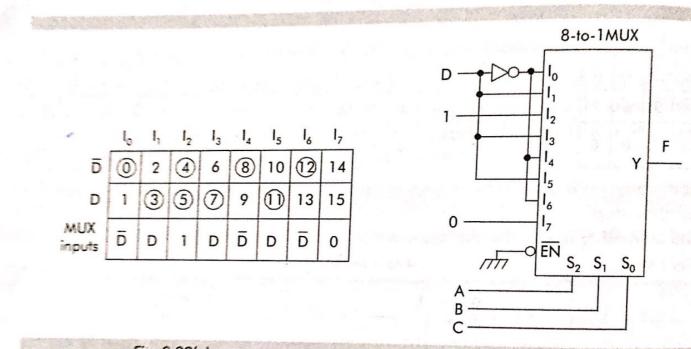

Implement the function  $F(A, B, C, D) = \overline{A}BD + \overline{B}CD + \overline{C}\overline{D}$  using MUX with the help of Implementation table. Use the least significant variable D as the input data variable for the MUX.

Solution This is a 4-variable function. Out of these four variables we have to use the least significant variable D as the data input variable leaving the variables A, B and C as the select variables. Therefore, we need one 8-to-1 MUX. The given function is converted into a canonical SOP form as follows

$$F(A, B, C, D) = \overline{A}BD + \overline{B}CD + \overline{C}\overline{D}$$

- $= \overline{A} B(C + \overline{C})D + (A + \overline{A})(\overline{B}CD) + (A + \overline{A})(B + \overline{B})\overline{C}\overline{D}$

- $= \overline{A}BCD + \overline{A}B\overline{C}D + A\overline{B}CD + \overline{A}BCD + AB\overline{C}\overline{D} + A\overline{B}\overline{C}\overline{D} +$

$\overline{A}B\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C}\overline{D}$

$= \sum m(0, 3, 4, 5, 7, 8, 11, 12)$

### 630 ♥ DIGITAL CIRCUITS

These minterms are plotted in the implementation table [Fig. 8.32 (a)] to get the 8 to 1 MUX. The corresponding circuit is shown in Fig. 8.32 (b).

Fig. 8.32(b)

## Decoder

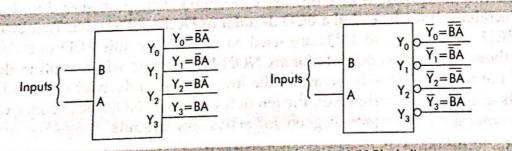

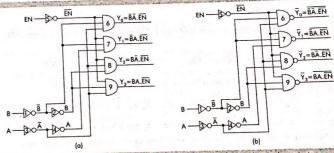

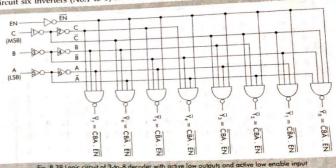

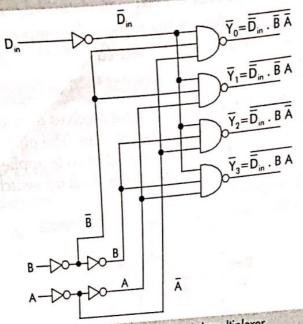

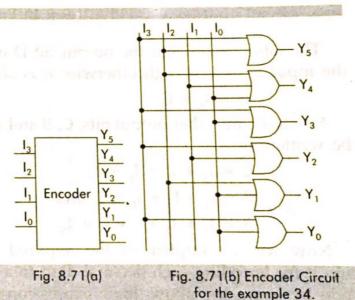

### 8.5.1 Introduction